# Preventing GaN Device VHF Oscillation APEC 2017

#### Zan Huang, Jason Cuadra

APEC 2017 | 1

### transphorm

Highest Performance, Highest Reliability GaN

# transphorm Parasitic oscillation

- Parasitic oscillation can occur in any switching circuit with fastchanging voltage and current that stimulate a parasitic LC network

- The oscillation becomes sustained when positive feedback with gain is present

- The feedback could be through parasitic capacitance, parasitic inductance, shared or coupling inductance, etc.

- Together with the device gain in the linear region, creates an oscillator

- Preventing oscillation in fast-switching GaN devices is more challenging than in silicon due to

- Faster dv/dt and di/dt

- Higher transconductance

- Violent sustained VHF oscillation (50-200MHz) will cause destruction

# transphorm Sustained oscillation

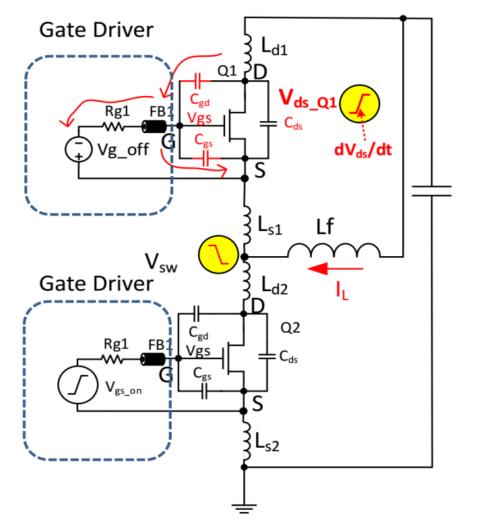

In a half-bridge circuit with high speed devices on both the high and low side, there are three steps that yield sustained oscillation on the high-side device during low-side device turn-on, and vice versa

Note: Sustained oscillation can occur even in a single-ended circuit, with very fast switching, e.g. a boost converter using a FET+diode; the analysis is similar to a half-bridge

# transphorm Step 1: V<sub>GS</sub> change due to high dv/dt

- During low-side turn-on, the high-side FET is subjected to a large positive dv/dt, which couples through C<sub>GD</sub> to increase V<sub>GS</sub>, ("Miller effect") reducing its off-voltage margin against gate threshold V<sub>TH</sub>

- To counter this, Transphorm devices are designed with a low ratio of C<sub>GD</sub> to C<sub>GS</sub> to minimize the Miller effect

# transphorm Step 2: V<sub>GS</sub> change due to high di/dt

- During low-side turn on, the high-side FET sees a decreasing current with a large negative di/dt, which multiplied by stray inductance L<sub>s</sub> in the PCB layout, produces a voltage V<sub>LS</sub>, and also reduces the off-voltage margin

- It is necessary to have a tight layout and minimize the stray inductance

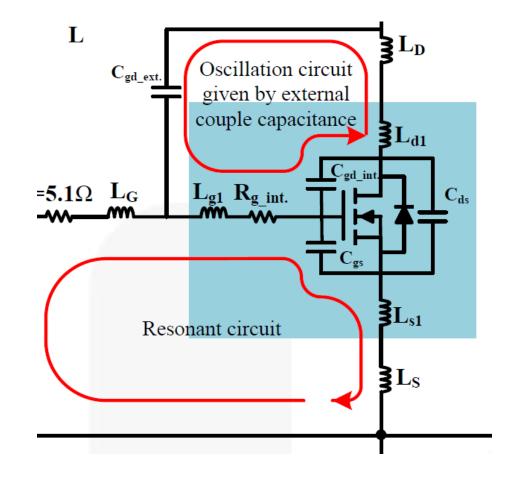

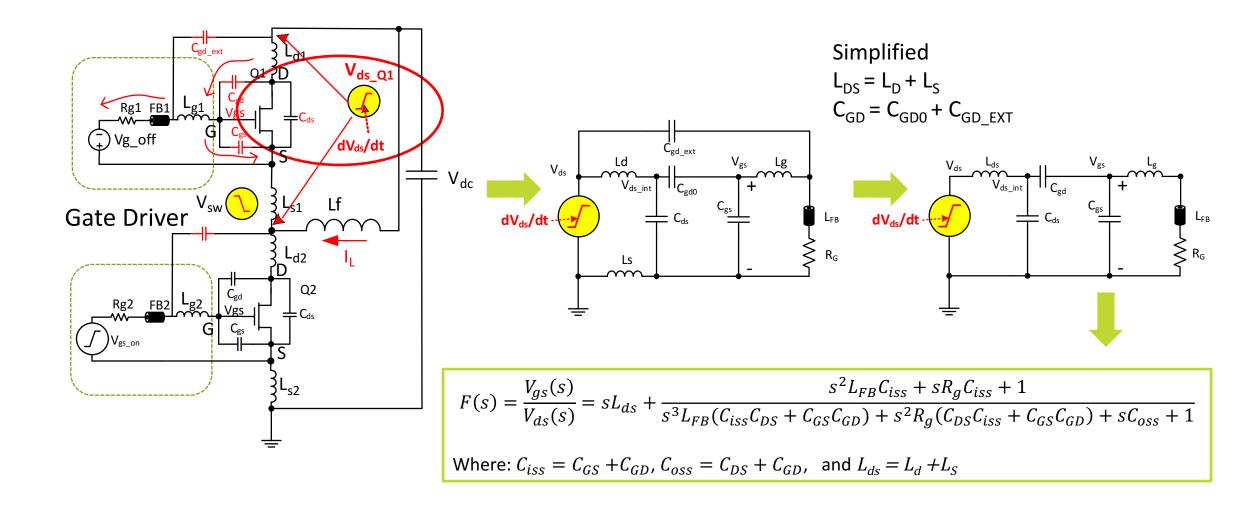

#### transphorm Step 3: Amplification due to transconductance

If V<sub>GS</sub> is pulled above the threshold voltage V<sub>TH</sub>, the device will operate in the linear region with transconductance g<sub>m</sub>, which can be defined in below equation:

The large gain in the feedback loop that includes external stray capacitance Cgd\_ext can then create a sustained oscillation

## transphorm The feedback loop transfer function

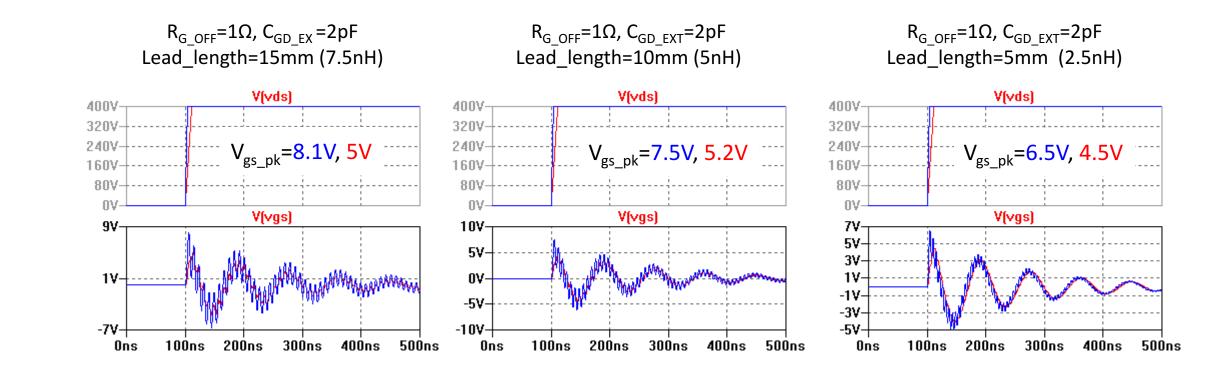

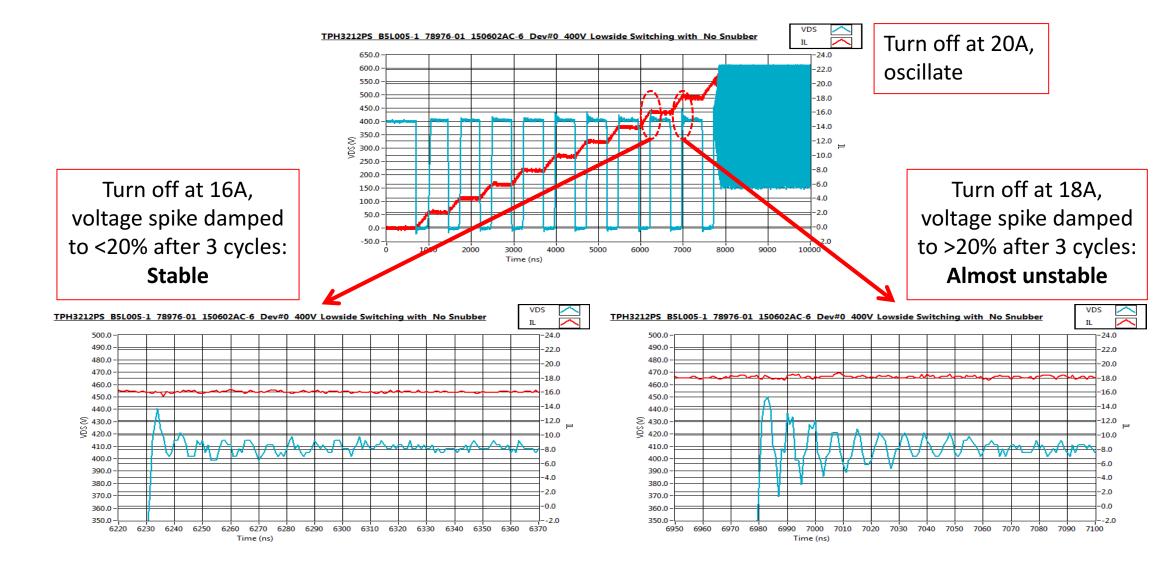

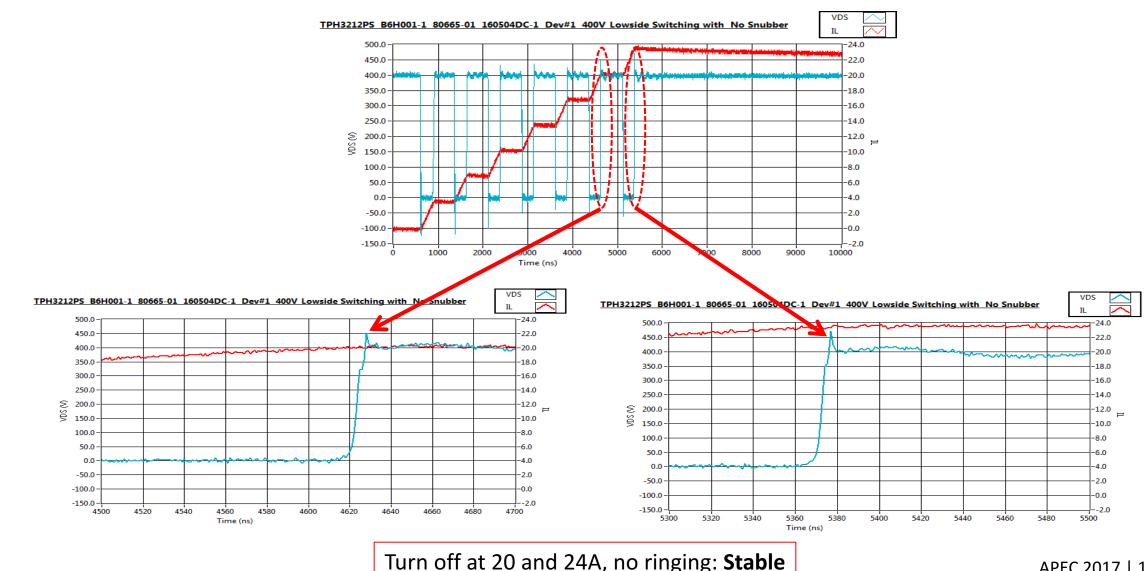

transphorm Comparing ringing amplitude

- Comparing blue and red curves, higher dV/dt increases the amplitude of the V<sub>GS</sub> ringing

- Comparing different parasitic inductances, higher inductances increases the amplitude of the V<sub>GS</sub> ringing

Red :  $dV_{DS}/dt=40V/ns$ Blue :  $dV_{DS}/dt=100V/ns$

### transphorm To suppress the sustained oscillation

- Required

- Optimize PCB layout

- Use a ferrite bead in the gate

- Highly recommended

- Add a ferrite bead to the drain

- Improves efficiency because excessive ringing is lossy

- Optional

- Add negative Vg\_off voltage

- Reduce the turn-on dv/dt

- Add an RC snubber to damp the ringing energy

- Slightly reduces efficiency

NOTE: The above can apply to a single-ended converter with very fast switching

#### **Choosing a Drain Ferrite Bead**

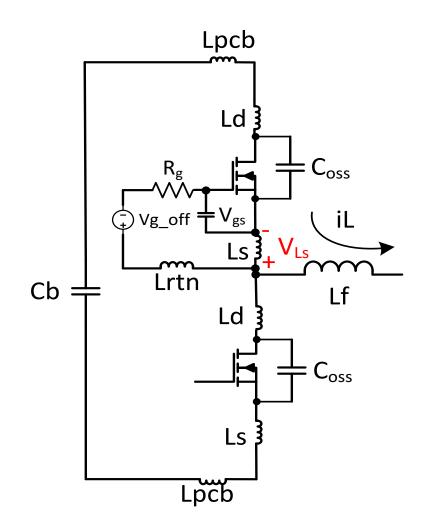

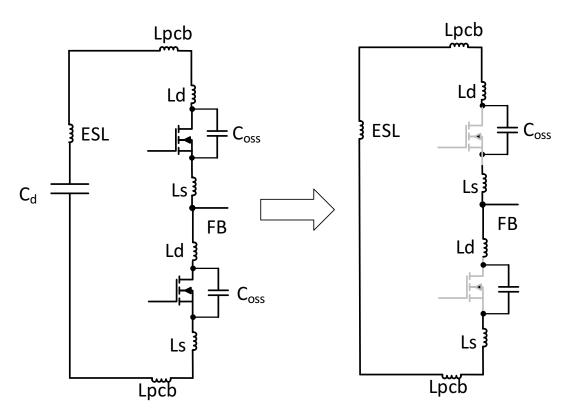

# transphorm Example: Bridge circuit

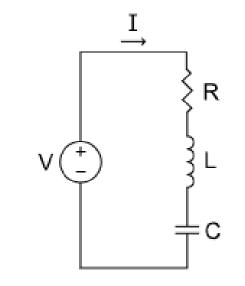

The equivalent LC resonant loop that largely determines the power loop oscillation frequency

$L = 2*L_{D} + 2*L_{S} + ESL + L_{PCB} + L_{WIRE}$

$C = C_{OSS}$ , (one  $C_{OSS}$  is bypassed when device is conducting)

## transphorm Adding the ferrite bead into the circuit

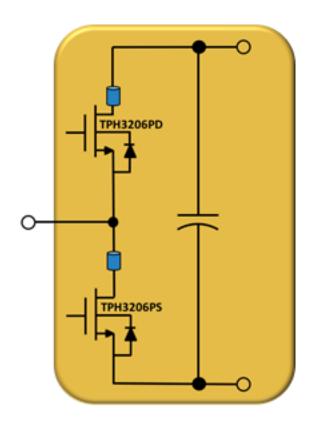

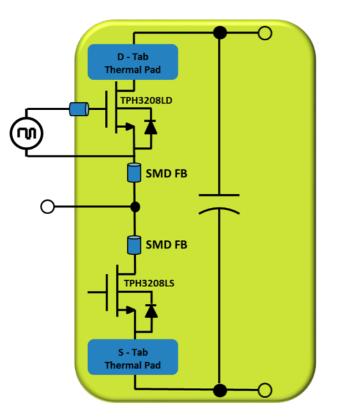

'Ring' (through-hole) type of the ferrite bead can be placed on through-hole type device's D pin

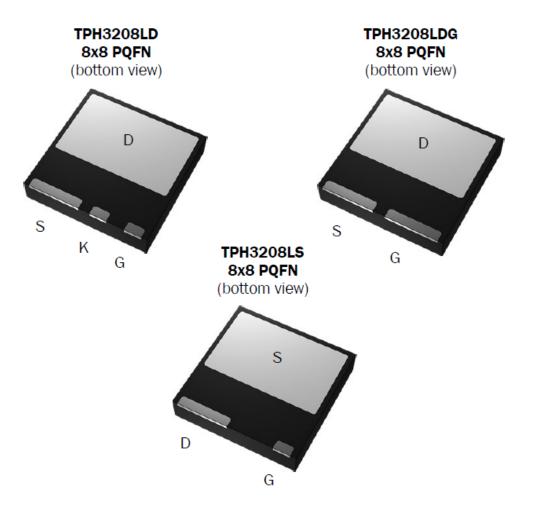

SMD type of ferrite bead should be placed on PCB without interfering with the heat dissipation from the large pad (drain for TPHxxxLD part, source for TPHxxxLS part)

#### transphorm **Transphorm PQFN Package Variations**

#### transphorm

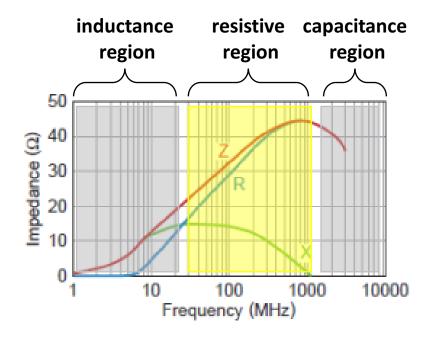

# Choose a ferrite bead as a damping resistor at the ringing frequency (50-200MHz)

For a series LCR circuit, the damping factor is given by:

$$\zeta = \frac{R}{2} \sqrt{\frac{C}{L}}$$

Choose the ferrite bead that R>X @50-200MHz, so the ferrite bead shows more resistive than inductive in this region For critical damping, R should be:

$$R = 2\zeta \sqrt{\frac{L}{C}} = 2 * 1 * \sqrt{\frac{25nH}{110pF}} = 30\Omega$$

So use a bead with >30 $\Omega$ @100MHz for each device

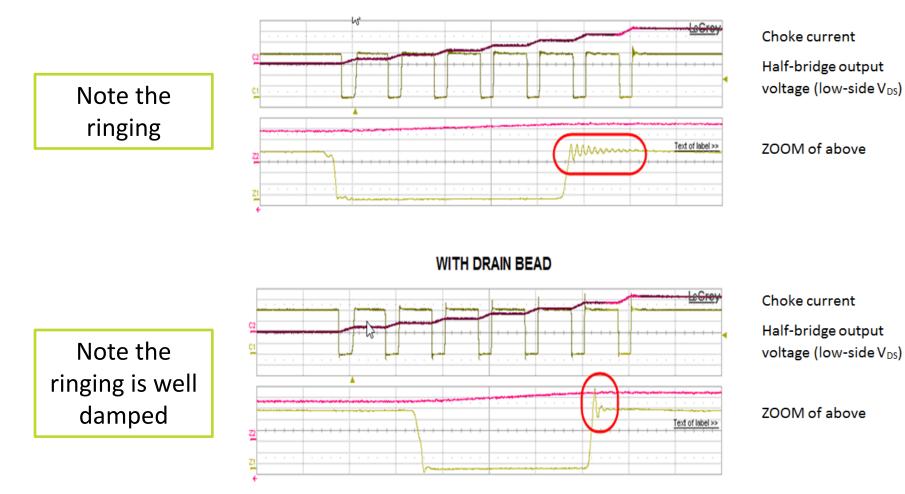

# transphorm Verifying the result

#### NO DRAIN BEAD

#### transphorm TPH3212 HB low side switching w/o FB

#### transphorm TPH3212 HB low side switching w/ FB

# transphorm V<sub>TDS</sub> rating

- Using a drain ferrite bead does increase the drain spike voltage

- However, all Transphorm devices are specified with  $V_{TDS}$  (transient  $V_{DS}$ ) which is 150V higher than the rated max DC  $V_{DS}$

- Transphorm devices are guaranteed to operate safely under repetitive spike voltages within the datasheet specification, making it more suitable for the drain ferrite bead solution

#### Absolute Maximum Ratings (Tc=25°C unless otherwise stated)

| Symbol             | Parameter                                |          | Limit Value | Unit |

|--------------------|------------------------------------------|----------|-------------|------|

| ID25*C             | Continuous drain current @Tc=25°C a      |          | 26.5        | Α    |

| ID100*C            | Continuous drain current @Tc=100°C a     |          | 16.5        | Α    |

| IDM                | Pulsed drain current (pulse width: 10µs) |          | 120         | А    |

| V <sub>DSS</sub>   | Drain to source voltage                  |          | 650         | V    |

| V <sub>TDS</sub>   | Transient drain to source voltage b      |          | 800         | V    |

| Vgss               | Gate to source voltage                   |          | ±18         | V    |

| PD25*C             | Maximum power dissipation                |          | 104         | w    |

| Tc                 | Operating temperature                    | Case     | -55 to +150 | °C   |

| T,                 |                                          | Junction | -55 to +150 | °C   |

| Ts                 | Storage temperature                      |          | -55 to +150 | °C   |

| T <sub>CSOLD</sub> | Soldering peak temperature °             |          | 260         | °C   |

#### **Thermal Resistance**

| Symbol           | Parameter           | Typical | Unit |

|------------------|---------------------|---------|------|

| Reuc             | Junction-to-case    | 1.2     | °C/W |

| R <sub>eja</sub> | Junction-to-ambient | 62      | °C/W |

| Notes:           |                     |         |      |

For high current operation, see application note AN000s In off-state, spike duty cycle D<0.01, spike duration <1µs For 10 sec., 1.6mm from the case b.

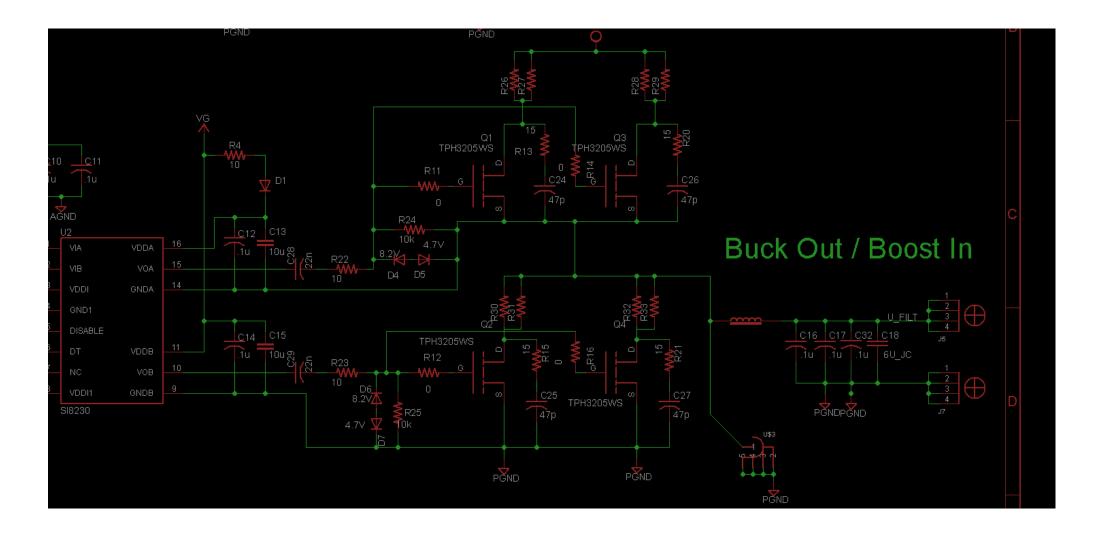

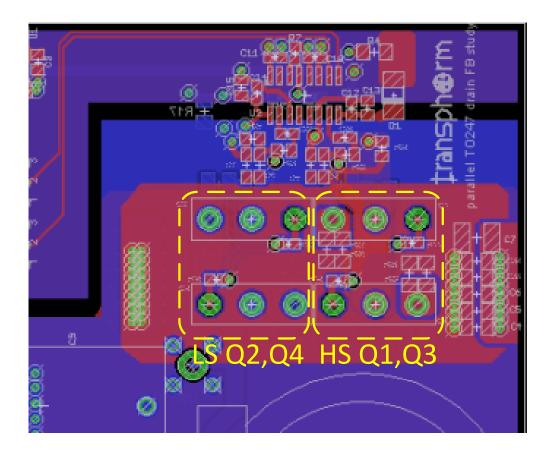

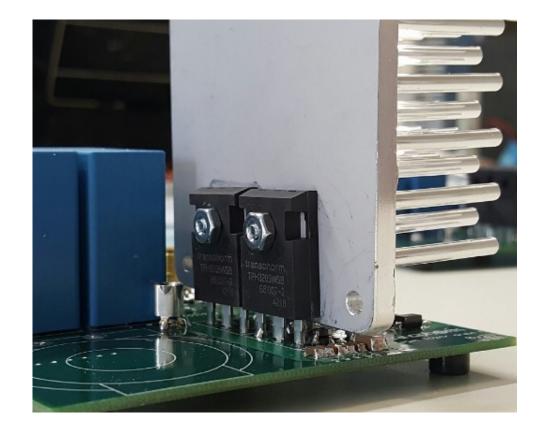

### transphorm Paralleling 650V/52mohm GaN with FB

## transphorm Layout with TO247 Packages

transphorm

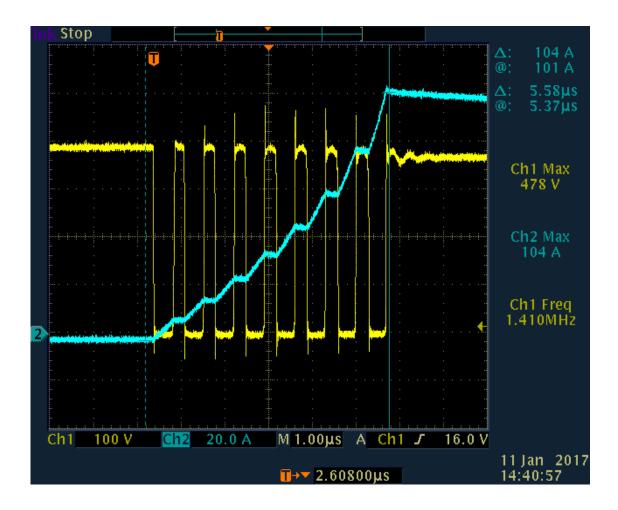

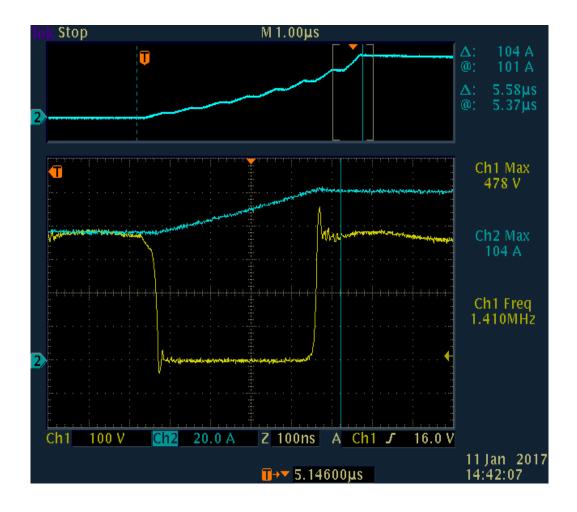

#### Switching 400V/100A with Clean Waveform

#### transphorm

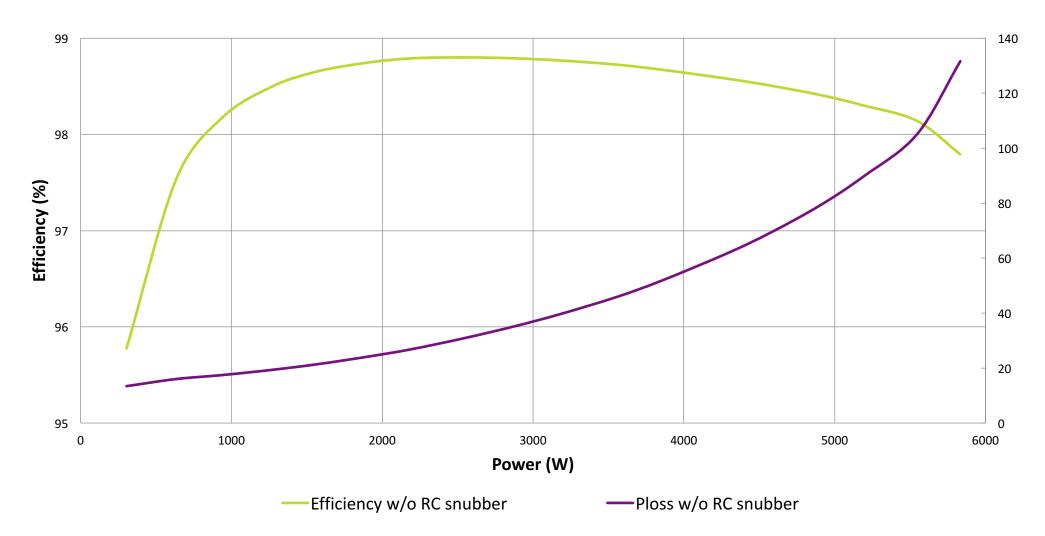

#### 200V:400V Boost Converter 5.5kW and 98.8% Peak Efficiency

#### **Thank You!**

# transphorm

Highest Performance, Highest Reliability GaN