# 1200V GaN Switches on Sapphire Substrate

G. Gupta<sup>1</sup>, M. Kanamura<sup>2</sup>, B. Swenson<sup>1</sup>, D. Bisi<sup>1</sup>, B. Romanczyk<sup>1</sup>, C. Neufeld<sup>1</sup>, S. Wienecke<sup>1</sup>, T. Ogino<sup>2</sup>, Y. Miyazaki<sup>2</sup>, K. Imanishi<sup>2</sup>, J. Ikeda<sup>2</sup>, M. Kamiyama<sup>2</sup>, J. Guerrero<sup>1</sup>, S. Yea<sup>1</sup>, M. Labrecque<sup>1</sup>, R. Prejdova<sup>1</sup>, B. Cruse<sup>1</sup>, J.

izaki<sup>-</sup>, K. Imanishi<sup>-</sup>, J. Ikeda<sup>-</sup>, M. Kamiyama<sup>+</sup>, J. Guerrero<sup>+</sup>, S. Fea<sup>+</sup>, M. Labrecque<sup>+</sup>, K. Frejdova<sup>+</sup>, B. Cruse<sup>+</sup>, J.

McKay<sup>1</sup>, G. Bolante<sup>1</sup>, Z. Wang<sup>1</sup>, T. Hosoda<sup>2</sup>, Y. Wu<sup>1</sup>, P. Parikh<sup>1</sup>, R. Lal<sup>1</sup>, U. Mishra<sup>1</sup>

<sup>1</sup>Transphorm, Inc., Goleta-CA, USA, email: <u>ggupta@transphormusa.com</u>

<sup>2</sup>Transphorm Japan, Shin-Yokohama, Japan

Abstract-We present results on 1200V GaN switches made with HEMTs on sapphire substrates. These are fast-switching, low loss devices extending the high performance of GaN switches to higher voltage levels. The insulating nature of sapphire substrates can help to extend the rated voltage of GaN HEMTs to 1200V and beyond, while simultaneously using a much thinner buffer laver compared to GaN-on-Si for similar voltages. Using a 70 m GaNon-sapphire 2-chip normally-off GaN FET in TO-247 package, we obtained >99% efficiency for a 900:450V buck converter operating at 50kHz. The GaN die has R<sub>ON,sp</sub> of 6.1mΩ.cm<sup>2</sup> and the device shows excellent switching FOMs with  $R_{ON}.Q_G = 0.9 \Omega.nC$ , and  $R_{ON}$ . QRR = 11  $\Omega$ .nC. The sapphire substrate is thinned to below 200µm to give a thermal resistance comparable to that of packaged GaN-on-Si switches. These results indicate that a correctly engineered GaN-on-sapphire technology can be a very competitive platform for the 1200V power device market.

## Keywords—GaN-on-sapphire, GaN-on-silicon, GaN-on-Si, 1200 V, low-loss, high-efficiency, switching FOM

## I. INTRODUCTION

GaN power switches have enabled higher efficiency and low system cost for power conversion applications due to the fastswitching and low losses in the switch [1][2]. State-of-the-art commercial GaN switches predominantly use silicon substrate and are fabricated in a GaN HEMT layer separated by a semiinsulating buffer from the substrate. 650V GaN-on-Si switches have achieved automotive qualification [3] and significant market acceptance [4] due to their superior performance compared to switches made with silicon or silicon carbide [5] at lower cost. 900V GaN-on-Si switches have also been released using lateral HEMT technology [6].

1200V GaN switches can enable similar performance improvements for applications such as EV drives, EV charging, PV inverters, and general 3-phase industrial applications [7]. 1200V rated devices on a GaN-on-Si platform would require use of very thick 10-12µm buffer layers, which adds significant cost and processing challenges [8]. GaN-on-engineered substrates [9], and GaN-on-GaN [10][11] research approaches have also been demonstrated but both require expensive >10µm epitaxial growth on expensive substrates. The insulating nature of sapphire reduces electric-fields in the semi-insulating buffer layers and enables 1200V devices with substantially thinner buffer layers than the 10-12µm expected for GaN-on-Si. This in turn reduces MOCVD growth cost, reduces stress in the underlying substrate and as a result can enable future scaling of substrate size to 200-mm or more for high throughput and lower manufacturing cost. 150-mm sapphire is widely used in the GaN

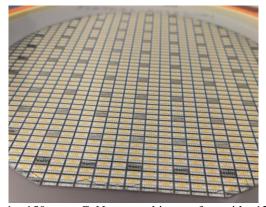

Fig. 1. 150-mm GaN-on-sapphire wafer with 1200V switches; thinned, diced and ready for packaging.

LED industry today and is low cost (< \$100) and recently 200mm sapphire has also become commercially available [12]. Backend and assembly of sapphire-based GaN devices are also well established and commercially available services. This makes sapphire very well suited as a substrate for GaN power switches.

In this paper, we demonstrate the viability of correctly engineered GaN-on-sapphire technology for 1200V power switches, and share comprehensive characterization of the devices including leakage, breakdown, dispersion, thermal resistance, inductive switching, and converter efficiency. We show how such a GaN-on-sapphire technology can be a strong enabler for voltage scaling of GaN HEMTs and high performance, manufacturable, low cost switches for 1200V and beyond.

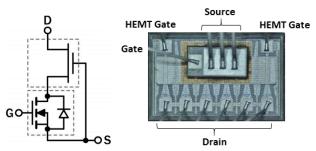

Fig. 2 (a) Circuit schematic of cascode switch configuration and (b) microscope image of the two-chip normally-off 1200V switch showing the die-on-die design and sapphire substrate directly bonded to the TO-247 package leadframe.

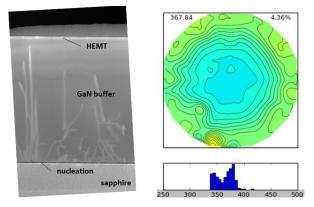

Fig. 3 (a) TEM cross-section of the GaN-on-sapphire epitaxy for 1200V switches, with low dislocation density near the active layers and (b) wafer level contactless  $R_{sh}$  showing median  $R_{sh}$  of 368  $\Omega$ /sq. and excellent  $R_{sh}$  uniformity of 4.4% over a 150-mm wafer (blue is lower  $R_{sh}$ ).

### II. DEVICE DESIGN AND CHARACTERISTICS

## A. Device design

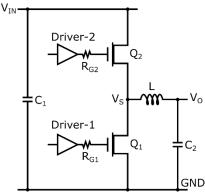

The semi-insulating GaN buffer (Fig. 3a) was heteroepitaxially grown on a 150-mm sapphire substrate using proprietary growth methodologies. The XRD FWHM values are excellent at 0.09° in 002 and 0.17° in 201 directions. This indicates very good material quality. Wafer level contactless sheet resistance measurement shows excellent uniformity of 4.36% (Fig. 3b). The 1200V devices were fabricated in a CMOS compatible wafer-fab line using process modules very similar to the established GaN-on-Si line, with sapphire thinning and dicing done on commercial tools (Fig. 1). A proprietary insulated field-plate architecture was used for electric-field management. This first generation device has a 16.59mm<sup>2</sup> die area and is designed to target a normally-off product with datasheet  $R_{ON}$  of 70m $\Omega$ . A 30V Si MOSFET is die attached on top of the GaN HEMT to realize the robust normally-off switch (Fig. 2). The Si MOSFET has a gate voltage rating of +/- 20V and Vth ~ 4V. This allows the device to be driven using standard gate drivers with a robust input interface.

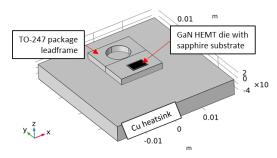

Fig. 6. 3D thermal model of GaN power HEMT in TO-247 package. Model estimate of Rth is in good agreement with measured Rth of 0.78°C/W

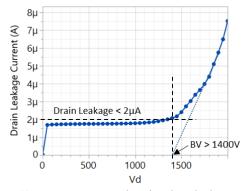

Fig 4. Off-state I-V curve, showing low leakage of  $< 2\mu A$  at 1200V and a breakdown voltage of more than 1400V.

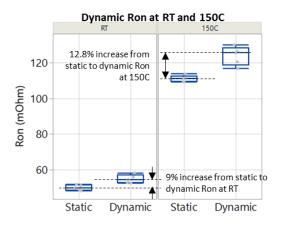

Fig. 5. Less than 10% increase in  $R_{ON}$  from static to dynamic conditions at RT and less than 13% at 150°C.

## B. Device Characteristics

The device leakage stays below  $2\mu A$  upto 1200V and device breakdown voltage is greater than 1400V (hard-breakdown voltage is even higher >2kV) giving an adequate voltage margin (Fig. 4). GaN-on-sapphire, due to its insulating nature, keeps vertical buffer fields minimal and enables large lateral blocking voltages with buffer thickness much less than that for GaN-on-Si. R<sub>ON,sp</sub> of this first generation GaN HEMT die is  $6.1m\Omega.cm^2$ .

To test the dynamic trapping behavior,  $R_{ON}$  of the devices was measured 1 µs after turn-ON following application of a blocking of 960V for 20ms in the OFF state (Fig. 5). The devices showed 9%  $R_{ON}$  increase compared to the static  $R_{ON}$ .  $R_{ON}$  increase under dynamic conditions at 150°C was 12.8% thus validating that the device design and epitaxial material quality are suitable for 1200 V switches in application (Fig. 5).

Junction-case thermal resistance  $(R_{th,j-c})$  is a key parameter for high-power devices. First, we modeled the thermal resistance of a die in a TO-247 package (Fig. 6) and identified that 100µm thick sapphire substrate can match the thermal resistance of a GaN-on-Si device. Based on this model, and as a first conservative step, the fabricated GaN-on-sapphire wafers were thinned down to 200µm and singulated. Thermal resistance measured on thinned, singulated, and packaged

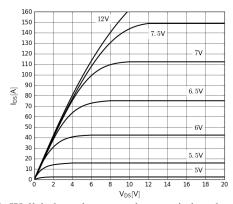

Fig. 7. Well behaved output characteristics showing very high pulsed current > 160A resulting from substrate thinning and thermal resistance of  $0.78^{\circ}$ C/W.

devices is  $0.78^{\circ}$ C/W and in good agreement with the predictions of the model. Substrate thinning to  $100\mu$ m (the target thickness) is well within the range offered by commercial vendors. Output characteristics of the device show high pulsed current > 160A (Fig. 7). This again shows that the device has good thermal characteristics and can achieve high current levels.

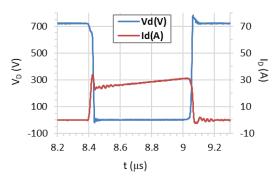

Fig. 9. Half-bridge inductive switching waveform at 720V/28A showing well behaved waveforms with tr ~ 14ns and tf ~ 13ns.

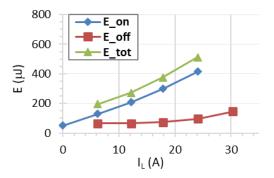

Fig. 10.  $E_{on}$ ,  $E_{off}$ , and  $E_{tot}$  extracted from 720V half-bridge inductive switching waveforms for 1200V GaN-on-sapphire device in TO-247 package.

| Switching FOMs                  | SoA SiC   | 1200V GaN |

|---------------------------------|-----------|-----------|

| R <sub>on</sub> Q <sub>G</sub>  | 4.3 Ω.nC  | 0.9 Ω.nC  |

| R <sub>ON</sub> Q <sub>RR</sub> | 19.2 Ω.nC | 11 Ω.nC   |

Fig. 8. 1200V GaN switching FOMs are superior to stateof-the-art 1200V SiC MOSFETs.

## III. FIGURE-OF-MERITS AND SWITCHING PERFORMANCE

#### A. Device FOMs and comparison to state-of-the-art

$Q_G$ ,  $Q_{OSS}$ , and  $Q_{RR}$  are key metrics that determines losses in hard-switched applications.  $Q_G$  is primarily determined by the Si MOSFET and is 15 nC for the MOSFET used here.  $Q_{OSS}$  of the device is 185 nC at 800 V.  $Q_{RR}$  is nominally the same as  $Q_{OSS}$ (185nC at 800V) since the stored minority charge in the device is negligible. The switching FOMs for the 1200V GaN-onsapphire device are:  $R_{ON}$ . $Q_G = 0.9 \Omega$ .nC,  $R_{ON}$ . $Q_{OSS} = 11 \Omega$ .nC, and  $R_{ON}$ . $Q_{RR} = 11 \Omega$ .nC. The switching FOMs of the 1200V GaN-on-sapphire device are excellent and the  $R_{ON}$ . $Q_G$  and  $R_{ON}$ . $Q_{RR}$  are better than state-of-the-art SiC devices (Fig. 8) [13]. Both wide-bandgap technologies have significantly better switching FOMs compared to silicon IGBTs and should perform much better in power switching applications.

#### B. Switching and converter efficiency

Inductive switching testing in a half-bridge circuit was performed at 720V/28A to capture the turn-on and turn-off transients (Fig. 9). Using an  $R_G = 47\Omega$ , the waveforms are well behaved and show fast rise and fall times  $t_r \sim 14$ ns and  $t_f \sim 13$ ns. The total losses increase at higher current levels as expected due to higher turn-on loss with the total switching losses being 510µJ per switching cycle at 720V/24A (Fig. 10).

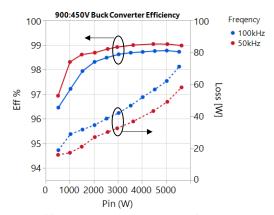

A 900:450V buck converter was built to test the efficiency of the devices at 50kHz and 100kHz (Fig. 11). Both high and lowside devices were GaN-on-sapphire  $1200V/70m\Omega$  devices. The circuit was operated in synchronous mode with dead time set appropriately to prevent shoot-through. During the turn-on transient, the inductor current is transferred from the reverse-

Fig. 11. Schematic circuit of 900:450V synchronous buck converter using two 1200V GaN switches (Q1/Q2) operated in hard-switched mode.

Fig. 12. Efficiency and power loss of a 900:450V buck converter operated at 50kHz and 100kHz in synchronous hard-switched mode. Peak efficiency is >99% at 50kHz and 98.7% at 100kHz.

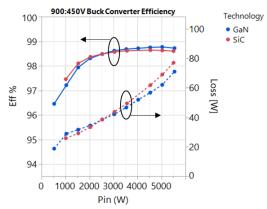

Fig. 13. Efficiency and power loss of a 900:450V buck converter operated at 100kHz in synchronous hard-switched mode. Peak efficiency of GaN is 98.76% vs 98.63% for SiC MOSFET.

conduction state of low-side device (Q1) to the high-side device (Q2). The Q<sub>OSS</sub> and Q<sub>RR</sub> of Q1 are also discharged through Q2 during this transition. Q2 therefore goes through a hardswitching event at every turn-on transition. The low Q<sub>OSS</sub> and Q<sub>RR</sub> of GaN-on-sapphire devices are key to achieving low switching loss. At a frequency of 100kHz, Q1 and Q2 are conducting for roughly 5µs each. 900:450V buck converter efficiency is > 99% at 50kHz and 98.7% at 100kHz (Fig. 12), which can be further optimized by reducing inductor losses. The low dynamic R<sub>ON</sub> was key to attaining the low conduction loss required to achieve the measured high efficiency. Buck converter efficiency using GaN-on-sapphire devices is higher than state-of-the-art SiC MOSFETs (Fig. 13). This result clearly demonstrates the promise of GaN-on-sapphire as a high-performance and low-cost 1200V solution.

# IV. CONCLUSION

GaN HEMTs on sapphire were designed and fabricated to extend the voltage range of lateral GaN FETs to 1200V. 1200V/70 m $\Omega$  GaN FETs were built using this GaN-on-sapphire technology and the performance was evaluated under various operating conditions. The devices demonstrated excellent leakage, dynamic R<sub>ON</sub>, and switching FOMs. 900:450V buck converter efficiency was > 99% when operated at 50kHz. The GaN-on-sapphire converter efficiency was better than state-of-the-art SiC MOSFETs owing to the superior switching FOMs. This work supports the promise of correctly engineered GaN-on-sapphire as a high-performance and low-cost solution for power conversion applications that require 1200V blocking voltage.

#### ACKNOWLEDGMENT

The authors gratefully acknowledge ARPA-E (Dr. Isik C. Kizilyalli) for funding part of this work (DE-AR0000890:-Subaward #: A18-0063-S001).

#### REFERENCES

- [1] Y.F. Wu, J. Gritters, L. Shen, R.P. Smith, J. McKay, R. Barr, R. Birkhahn, "Performance and robustness of first generation 600-V GaN-on-Si power transistors", The 1st IEEE Workshop on Wide Bandgap Power Devices and Applications, 6-10, Oct, 2013.

- [2] P. Parikh, Y.F. Wu, L.K. Shen, "Commercialization of High 600V GaNon-Silicon Power Devices", Materials Science Forum, Vols. 778-780, pp. 1174-1179, October 2014.

- [3] P. Parikh et al., "650 Volt GaN Commercialization Reaches Automotive Standards", ECS Trans. 80 17, 2017.

- [4] <u>http://www.semiconductor-today.com/news\_items/2020/mar/yole-230320.shtml</u>

- [5] https://www.transphormusa.com/en/gan-technology/

- [6] <u>https://www.transphormusa.com/en/news/transphorm\_900v\_geniii\_gan\_fet/</u>

- [7] <u>http://www.semiconductor-today.com/news\_items/2021/mar/yole-180321.shtml</u>

- [8] F. Semond, "Epitaxial challenges of GaN on silicon." MRS Bulletin 40.5 (2015): 412-417.

- [9] <u>http://www.semiconductor-today.com/news\_items/2021/apr/aixtronimec-290421.shtml</u>

- [10] Nie et al., "1.5-kV and 2.2-m-cm2 Vertical GaN Transistors on Bulk-GaN Substrates", IEEE Electron Device Letters, Vol. 35, No. 9, 2014

- [11] Ji et al., "Demonstrating >1.4 kV OG-FET performance with a novel double field-plated geometry and the successful scaling of large-area devices", IEDM, 2017

- [12] https://global.kyocera.com/prdct/fc/product/pdf/s\_c\_sapphire.pdf

- [13] https://cms.wolfspeed.com/app/uploads/2021/05/E3M0075120D.pdf